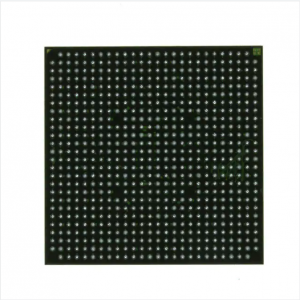

इलेक्ट्रोनिक अवयव मूल IC चिप BOM सूची सेवा BGA668 XC4VLX25-10FFG668C IC FPGA 448 I/O 668FCBGA

उत्पादन विशेषताहरू

| TYPE | DESCRIPTION |

| श्रेणी | एकीकृत सर्किट (ICs) इम्बेडेड FPGAs (फिल्ड प्रोग्रामेबल गेट एरे) |

| Mfr | AMD Xilinx |

| शृङ्खला | Virtex®-4 LX |

| प्याकेज | ट्रे |

| मानक प्याकेज | 1 |

| उत्पादन स्थिति | सक्रिय |

| LABs/CLB को संख्या | २६८८ |

| तर्क तत्व/सेलहरूको संख्या | 24192 |

| कुल RAM बिट्स | १३२७१०४ |

| I/O को संख्या | ४४८ |

| भोल्टेज - आपूर्ति | 1.14V ~ 1.26V |

| माउन्टिङ प्रकार | सतह माउन्ट |

| सञ्चालन तापमान | 0°C ~ 85°C (TJ) |

| प्याकेज / केस | 668-BBGA, FCBGA |

| आपूर्तिकर्ता उपकरण प्याकेज | 668-FCBGA (27×27) |

| आधार उत्पादन नम्बर | XC4VLX25 |

नवीनतम विकासहरू

Xilinx को विश्वको पहिलो 28nm Kintex-7 को आधिकारिक घोषणा पछि, कम्पनीले भर्खरै पहिलो पटक चार 7 श्रृंखला चिप्स, Artix-7, Kintex-7, Virtex-7, र Zynq को विवरण र वरपरका विकास स्रोतहरू प्रकट गरेको छ। 7 श्रृंखला।

सबै 7 शृङ्खलाका FPGA हरू एकीकृत वास्तुकलामा आधारित छन्, सबै 28nm प्रक्रियामा छन्, जसले ग्राहकहरूलाई कार्यसम्पादन र क्षमता बढाउँदै लागत र बिजुली खपत कम गर्न कार्यात्मक स्वतन्त्रता दिन्छ, जसले गर्दा कम लागत र उच्च-लागतको विकास र तैनातीमा लगानी घटाउँछ। प्रदर्शन परिवारहरू।वास्तुकला उच्च सफल Virtex-6 वास्तुकलाको परिवारमा बनाइएको छ र हालको Virtex-6 र Spartan-6 FPGA डिजाइन समाधानहरूको पुन: प्रयोगलाई सरल बनाउन डिजाइन गरिएको हो।वास्तुकला पनि प्रमाणित EasyPath द्वारा समर्थित छ।FPGA लागत घटाउने समाधान, जसले वृद्धिशील रूपान्तरण वा ईन्जिनियरिङ् लगानी बिना 35% लागत कटौती सुनिश्चित गर्दछ, उत्पादकता थप बढाउँछ।

एन्डी नोर्टन, क्लाउडशील्ड टेक्नोलोजीमा सिस्टम आर्किटेक्चरका लागि CTO, एक SAIC कम्पनीले भने: "6-LUT आर्किटेक्चरलाई एकीकृत गरेर र AMBA स्पेसिफिकेशनमा ARM सँग काम गरेर, Ceres ले यी उत्पादनहरूलाई IP पुन: प्रयोग, पोर्टेबिलिटी, र भविष्यवाणीलाई समर्थन गर्न सक्षम बनाएको छ।एक एकीकृत वास्तुकला, एक नयाँ प्रोसेसर-केन्द्रित उपकरण जसले मानसिकता परिवर्तन गर्दछ, र अर्को पुस्ताका उपकरणहरूसँग स्तरित डिजाइन प्रवाहले उत्पादकता, लचिलोपन, र प्रणाली-अन-चिप कार्यसम्पादनमा नाटकीय रूपमा सुधार मात्र गर्दैन, तर अघिल्लो माइग्रेसनलाई पनि सरल बनाउँदछ। वास्तुकला को पुस्ता।अधिक शक्तिशाली SOC हरू उन्नत प्रक्रिया प्रविधिहरूको लागि धन्यवाद निर्माण गर्न सकिन्छ जसले ऊर्जा खपत र कार्यसम्पादनमा महत्त्वपूर्ण प्रगति गर्न अनुमति दिन्छ, र केही चिपहरूमा A8 प्रोसेसर हार्डकोर समावेश गर्दछ।

Xilinx विकास इतिहास

अक्टोबर 24, 2019 - Xilinx (XLNX.US) FY2020 Q2 राजस्व 12% YoY, Q3 कम्पनीको लागि न्यून बिन्दु हुने अपेक्षा गरिएको छ

डिसेम्बर 30, 2021, AMD को $ 35 बिलियन Ceres को अधिग्रहण 2022 मा बन्द हुने अपेक्षा गरिएको छ, पहिलेको योजना भन्दा पछि।

जनवरी २०२२ मा, बजार पर्यवेक्षणको सामान्य प्रशासनले थप प्रतिबन्धात्मक सर्तहरूको साथ यो अपरेटर एकाग्रतालाई अनुमोदन गर्ने निर्णय गर्यो।

14 फेब्रुअरी 2022 मा, AMD ले घोषणा गर्यो कि यसले सेरेसको अधिग्रहण पूरा गरेको छ र सेरेस बोर्डका पूर्व सदस्यहरू जोन ओल्सन र एलिजाबेथ भान्डरस्लाइस AMD बोर्डमा सामेल भएका थिए।