इलेक्ट्रोनिक आईसी चिप समर्थन BOM सेवा TPS54560BDDAR ब्रान्ड नयाँ आईसी चिप्स इलेक्ट्रोनिक्स घटकहरू

उत्पादन विशेषताहरू

| TYPE | DESCRIPTION |

| श्रेणी | एकीकृत सर्किट (ICs) |

| Mfr | टेक्सास उपकरण |

| शृङ्खला | इको-मोड™ |

| प्याकेज | टेप र रिल (TR) कट टेप (CT) Digi-Reel® |

| SPQ | 2500T&R |

| उत्पादन स्थिति | सक्रिय |

| समारोह | स्टेप-डाउन |

| आउटपुट कन्फिगरेसन | सकारात्मक |

| टोपोलोजी | बक, स्प्लिट रेल |

| आउटपुट प्रकार | समायोज्य |

| आउटपुटहरूको संख्या | 1 |

| भोल्टेज - इनपुट (न्यूनतम) | ४.५V |

| भोल्टेज - इनपुट (अधिकतम) | ६०V |

| भोल्टेज - आउटपुट (न्यूनतम/निश्चित) | ०.८V |

| भोल्टेज - आउटपुट (अधिकतम) | ५८.८V |

| वर्तमान - आउटपुट | 5A |

| आवृत्ति - स्विचिंग | 500kHz |

| सिंक्रोनस रेक्टिफायर | No |

| सञ्चालन तापमान | -40°C ~ 150°C (TJ) |

| माउन्टिङ प्रकार | सतह माउन्ट |

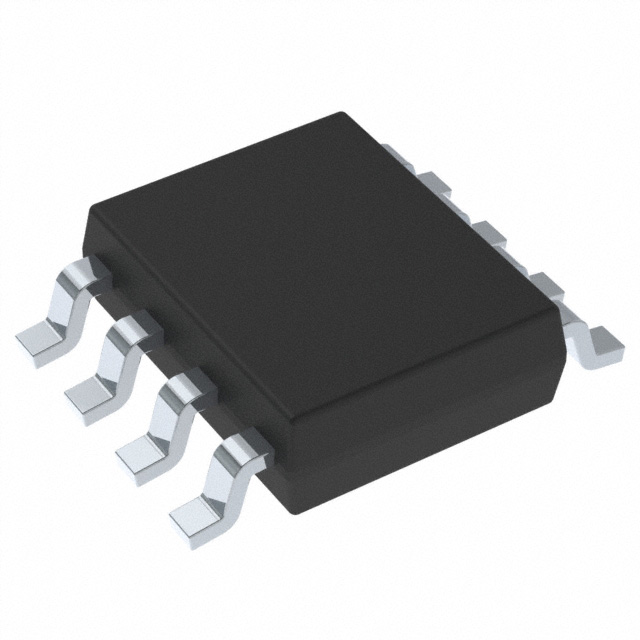

| प्याकेज / केस | 8-PowerSOIC (0.154", 3.90mm चौडाइ) |

| आपूर्तिकर्ता उपकरण प्याकेज | 8-SO PowerPad |

| आधार उत्पादन नम्बर | TPS54560 |

1.आईसी नामकरण, प्याकेज सामान्य ज्ञान र नामकरण नियमहरू:

तापमान सीमा।

C=0°C देखि 60°C (व्यावसायिक ग्रेड);I=-20°C देखि 85°C (औद्योगिक ग्रेड);E=-40°C देखि 85°C (विस्तारित औद्योगिक ग्रेड);A=-40°C देखि 82°C (एरोस्पेस ग्रेड);M=-55°C देखि 125°C (सैन्य ग्रेड)

प्याकेज प्रकार।

A-SSOP;B-CERQUAD;C-TO-200, TQFP;D-सिरेमिक तामा शीर्ष;E-QSOP;F-सिरेमिक SOP;H- SBGAJ-सिरेमिक DIP;K-TO-3;L-LCC, M-MQFP;N-संकीर्ण DIP;N-DIP;Q PLCC;R - संकीर्ण सिरेमिक DIP (300mil);S - TO-52, T - TO5, TO-99, TO-100;U - TSSOP, uMAX, SOT;W - चौडा सानो फारम कारक (300mil) W-वाइड सानो फारम कारक (300 mil);X-SC-60 (3P, 5P, 6P);Y-संकीर्ण तामा शीर्ष;Z-TO-92, MQUAD;डी-डाइ;/PR-प्रबलित प्लास्टिक;/W-Wafer।

पिन संख्या:

a-8;b-10;c-12, 192;d-14;e-16;f-22, 256;g-4;h-4;i -4;H-4;I-28;J-2;K-5, 68;L-40;M-6, 48;N 18;O-42;P-20;Q-2, 100;R-3, 843;S-4, 80;T-6, 160;U-60 -6,160;U-60;V-8 (गोल);W-10 (गोल);X-36;Y-8 (गोल);Z-10 (गोल)।(गोलो)।

नोट: इन्टरफेस वर्गको चार अक्षरको प्रत्ययको पहिलो अक्षर E हो, जसको मतलब उपकरणमा antistatic प्रकार्य छ।

2.प्याकेजिङ प्रविधिको विकास

प्रारम्भिक एकीकृत सर्किटहरूले सिरेमिक फ्ल्याट प्याकेजहरू प्रयोग गर्थे, जुन तिनीहरूको विश्वसनीयता र सानो आकारको कारण धेरै वर्षसम्म सेनाले प्रयोग गरिरह्यो।कमर्शियल सर्किट प्याकेजिङ चाँडै सिरेमिक र त्यसपछि प्लास्टिकबाट सुरु हुँदै दोहोरो इन-लाइन प्याकेजहरूमा सर्यो, र 1980 को दशकमा VLSI सर्किटहरूको पिन काउन्टले DIP प्याकेजहरूको आवेदन सीमा नाघ्यो, जसले अन्ततः पिन ग्रिड एरे र चिप क्यारियरहरूको उदय भयो।

सतह माउन्ट प्याकेज प्रारम्भिक 1980 मा देखा पर्यो र त्यो दशकको पछिल्लो भागमा लोकप्रिय भयो।यसले राम्रो पिन पिच प्रयोग गर्दछ र गुल-पिङ वा J-आकारको पिन आकार छ।Small-Outline Integrated Circuit (SOIC), उदाहरणका लागि, 30-50% कम क्षेत्र छ र बराबर DIP भन्दा 70% कम बाक्लो छ।यो प्याकेजमा गुल-पखेटा-आकारको पिनहरू दुई लामो छेउबाट फैलिएको छ र ०.०५" को पिन पिच छ।

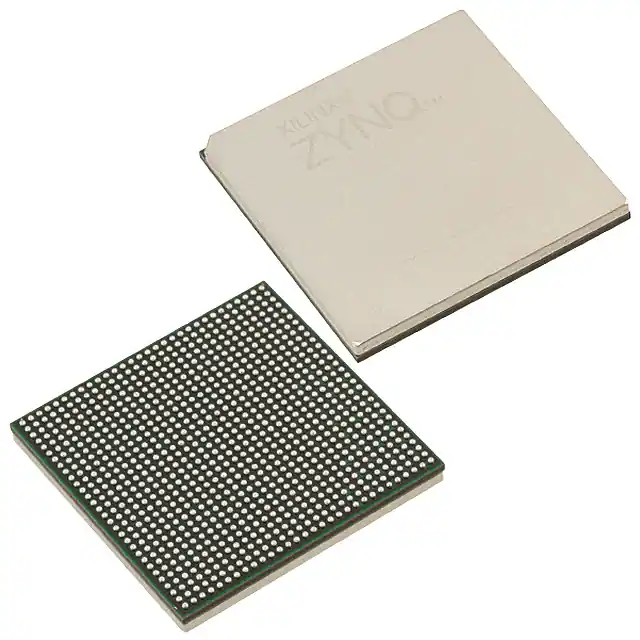

Small-Outline Integrated Circuit (SOIC) र PLCC प्याकेजहरू।1990 मा, यद्यपि PGA प्याकेज अझै पनि उच्च-अन्त माइक्रोप्रोसेसरहरूको लागि प्रयोग गरिन्थ्यो।PQFP र पातलो सानो-आउटलाइन प्याकेज (TSOP) उच्च पिन गणना उपकरणहरूको लागि सामान्य प्याकेज भयो।Intel र AMD को उच्च-अन्त माइक्रोप्रोसेसरहरू PGA (पाइन ग्रिड एरे) प्याकेजहरूबाट ल्यान्ड ग्रिड एरे (LGA) प्याकेजहरूमा सारियो।

बल ग्रिड एरे प्याकेजहरू 1970 को दशकमा देखा पर्न थाले, र 1990 को दशकमा FCBGA प्याकेज अन्य प्याकेजहरूको तुलनामा उच्च पिन गणनाको साथ विकसित गरिएको थियो।FCBGA प्याकेजमा, डाइलाई माथि र तल फ्लिप गरिन्छ र प्याकेजमा रहेको सोल्डर बलहरूमा तारहरूको सट्टा PCB-जस्तो आधार तहद्वारा जडान गरिन्छ।आजको बजारमा, प्याकेजिङ पनि अब प्रक्रियाको एक अलग भाग हो, र प्याकेजको प्रविधिले उत्पादनको गुणस्तर र उपजलाई पनि असर गर्न सक्छ।